#### **ASYNCHRONOUS SEQUENTIAL CIRCUITS**

- Sequential circuits that are not synchronized by a clock – Asynchronous circuits

- Analysis of Asynchronous circuits

- Synthesis of Asynchronous circuits

- Hazards that cause incorrect behavior of a circuit

# **ASYNCHRONOUS SEQUENTIAL CIRCUITS**

- Synchronous sequential circuits

- > state variables : F/Fs

- $\succ$  controlled by a clock

- ➢ operate in pulse mode

- Asynchronous sequential circuits

- ➤ do not operate in synchronous with *clock signal*.

- > do not use F/Fs to represent state variables

- Changes in state are dependent on whether each of inputs to the circuit has the logic level 0 or 1 at any given time

- To achieve reliable operation

- > the inputs to the circuit must change one at a time

- there must be sufficient time between the changes in input signals to allow the circuit to reach a stable state

- A circuit that adheres to these constraints is said to operate in the *fundamental* mode

**Advantages of Asynchronous Circuits**

- No clock skew (clock signal arrives at different time)

- Lower power (Synchronous : clock signal must be present every time and everywhere.

- Average-case performance VS worstcase performance

- Easing of global timing issues

- Partial optimization

- Better external input handling

DRAWBACKS

More difficult to design

Concerns for hazards and glitches

Unsure about faster performance

# WHY ASYNCHRONOUS CIRCUITS ?

- Used when speed of operation is important

- Response quickly without waiting for a clock pulse

- Used in small independent systems

- > Only a few components are required

- Used when the input signals may change independently of internal clock

- >Asynchronous in nature

- Used in the communication between two units that have their own independent clocks

- > Must be done in an asynchronous fashion

## **MODE OF OPERATIONS**

#### Steady-state condition:

- Current states and next states are the same

- Difference between Y and y will cause a transition

#### Fundamental mode:

- > No simultaneous changes of two or more variables

- The time between two input changes must be longer than the time it takes the circuit to a stable state

- The input signals change one at a time and only when the circuit is in a stable condition Fundamental Mode

#### Pulse Mode:

- $\succ$  the inputs and outputs are represented by pulses.

- > only one input is allowed to have pulse present at any time.

- Similar to synchronous sequential circuits except without a clock signal.

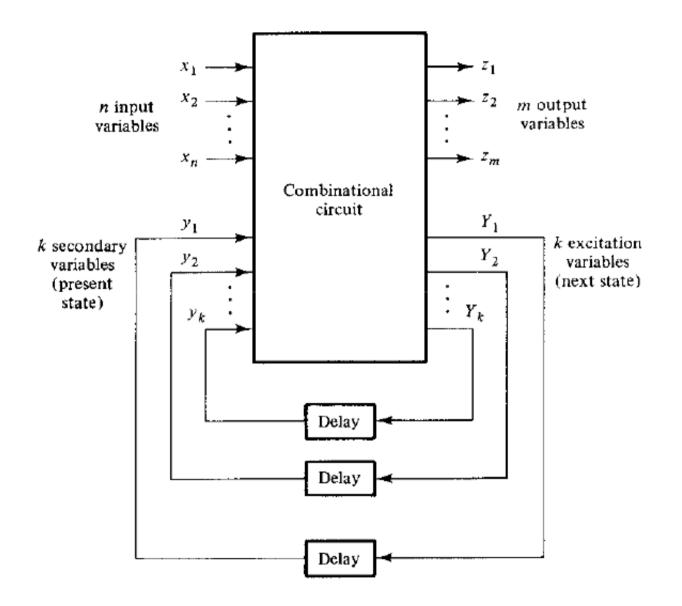

#### **GENERAL BLOCK DIAGRAM**

7

#### TERMINOLOGY

# Asynchronous circuits

- > state table -> flow table

- > state-assigned table -> transition table

or excitation table

- will use the term flow table and excitation table

#### **STEPS IN THE ANALYSIS PROCESS**

# Each feedback path is cut

- A delay element is inserted at the point where the cut is made

- A cut can be made anywhere in a particular loop formed by feedback connection, as long as there is only one cut per (state variable) loop

- Next-state and output expressions are derived from the circuit

- The excitation table is derived

- A flow table is obtained

- A corresponding state diagram is derived from the flow table if desired

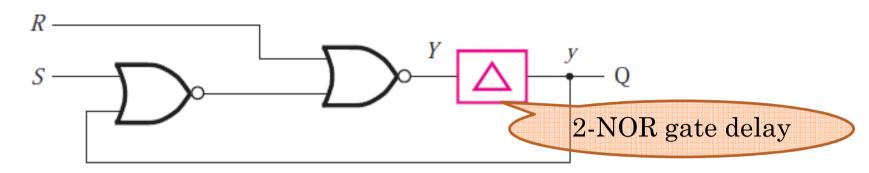

## **ASYNCHRONOUS BEHAVIOR OF SR-LATCH**

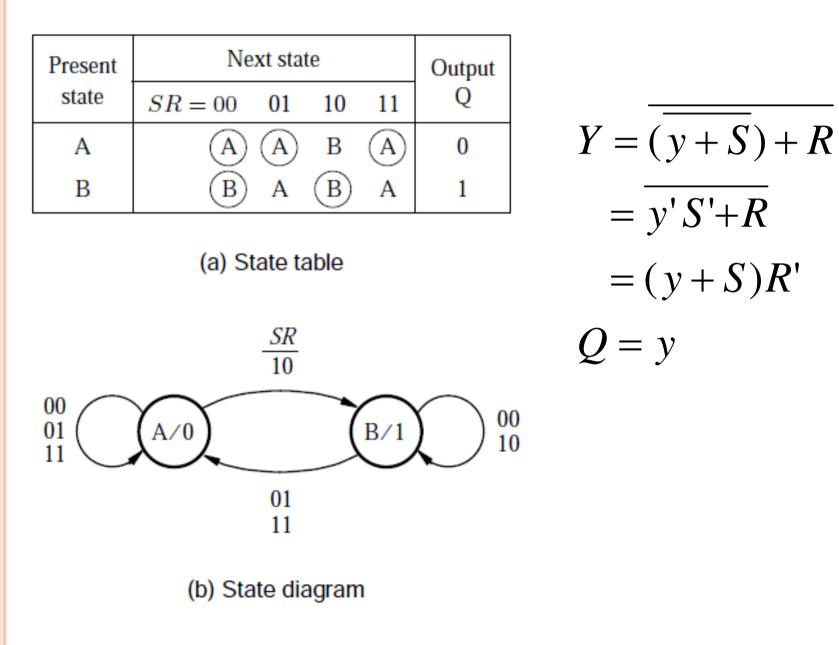

$$Y = (\overline{y+S}) + R$$

$$= y'S' + R = (y+S)R$$

**Stable** state: given inputs, if a circuit reaches a state and remains in that state, then the state is said to be "<u>stable</u>".

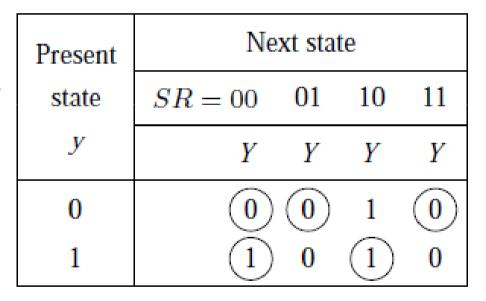

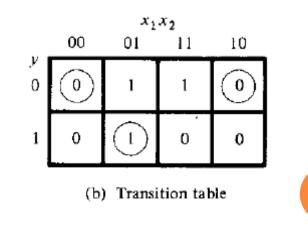

#### (b) State-assigned table

Circles denote "stable" states, i.e., state "unchanged".

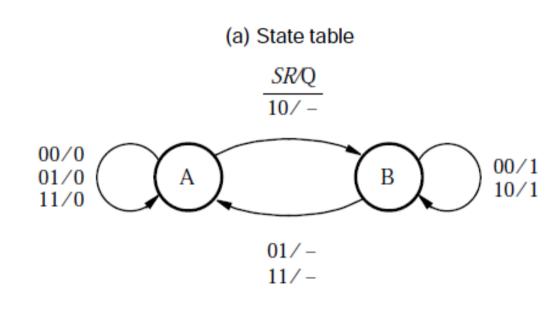

#### MOORE FSM MODEL

#### MEALY FSM

| Present | Next state |    |    | Outp           | ut, Q |    |    |    |

|---------|------------|----|----|----------------|-------|----|----|----|

| state   | SR = 00    | 01 | 10 | 11             | 00    | 01 | 10 | 11 |

| Α       | A          | A  | В  | $(\mathbf{A})$ | 0     | 0  | _  | 0  |

| В       | В          | А  | B  | А              | 1     | _  | 1  | _  |

<u>Unspecified output</u>: At state A: input 10 changes to state B, Y=1, Q=1 after reaching state B. No need to change it beforehand.

(b) State diagram

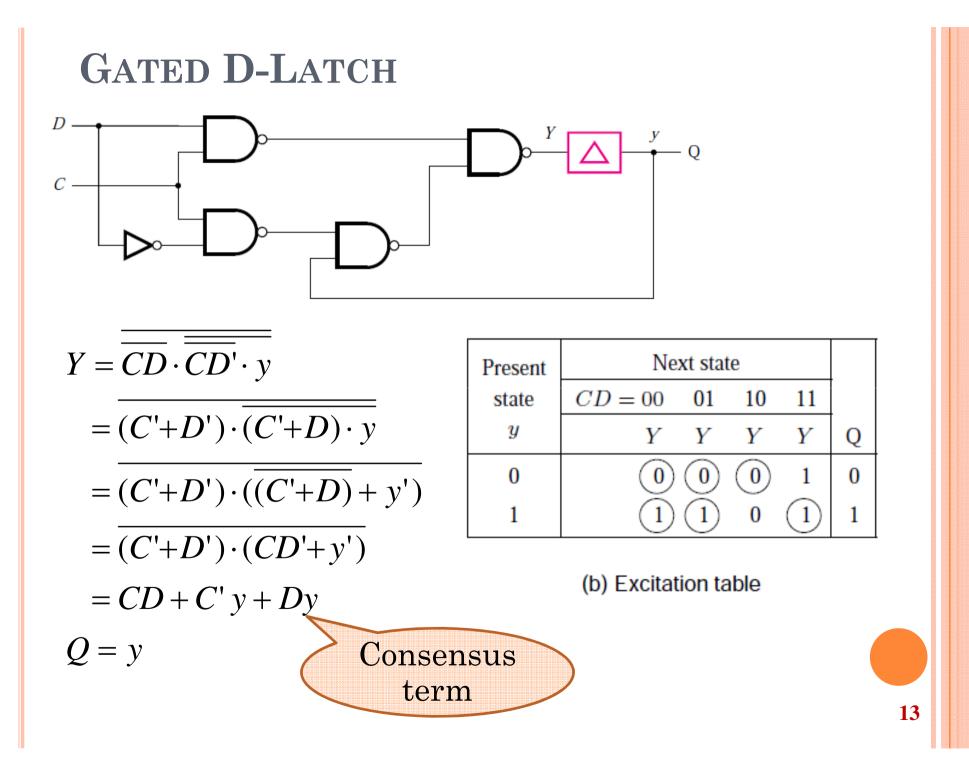

#### GATED D-LATCH (2)

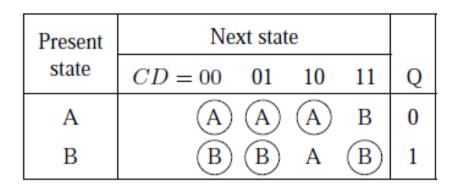

(c) Flow table

(d) State diagram

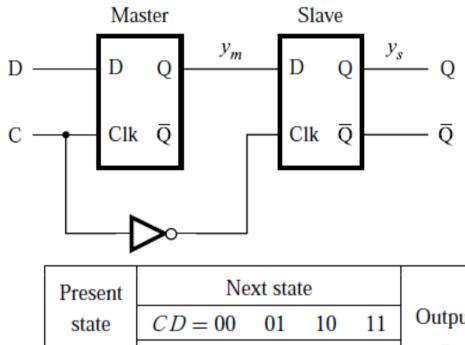

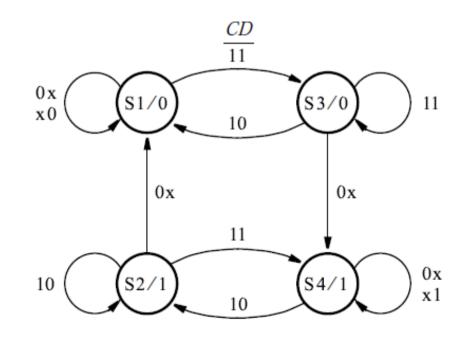

#### MASTER-SLAVE D FLIP-FLOP

$$Y_m = CD + C' y_m$$

$$Y_s = C' y_m + C y_s$$

$$Q = y_s$$

Output Q Ym Ys  $Y_m Y_s$ (00)(00)(00)10 00 0 (01)01 00 00 11 1 (10)11 00 0 10 11 (11) (11)01 (11)11 1

(a) Excitation table

#### MASTER-SLAVE D FLIP-FLOP (2)

| Present | Ne           | Next state   |              |                  |   |

|---------|--------------|--------------|--------------|------------------|---|

| state   | CD = 00      | 01           | 10           | 11               | Q |

| S1      | <u>(S1)</u>  | <u>(S1</u> ) | <u>(S1</u> ) | S3               | 0 |

| S2      | S1           | S1           | <u>(S2</u> ) | S4               | 1 |

| S3      | S4           | S4           | S1           | <b>S</b> 3       | 0 |

| S4      | <u>(S4</u> ) | <u>(S4</u> ) | S2           | $\widetilde{S4}$ | 1 |

| Present    | Next state   |              |              |            | Output |

|------------|--------------|--------------|--------------|------------|--------|

| state      | CD = 00      | 01           | 10           | 11         | Q      |

| S1         | <u>(S1)</u>  | <u>(S1</u> ) | <u>(S1</u> ) | S3         | 0      |

| S2         | S1           | _            | <u>S2</u>    | S4         | 1      |

| <b>S</b> 3 | _            | S4           | S1           | <b>S</b> 3 | 0      |

| S4         | <u>(S4</u> ) | <u>(S4</u> ) | S2           | <u>Š4</u>  | 1      |

(b) Flow table

(c) Flow table with unspecified entries

<u>Unspecified entries</u>: At state S2: stable with input CD=10. Thus, cannot achieve CD=01. (2 inputs cannot change at the same time.)

#### FURTHER EXAMPLE

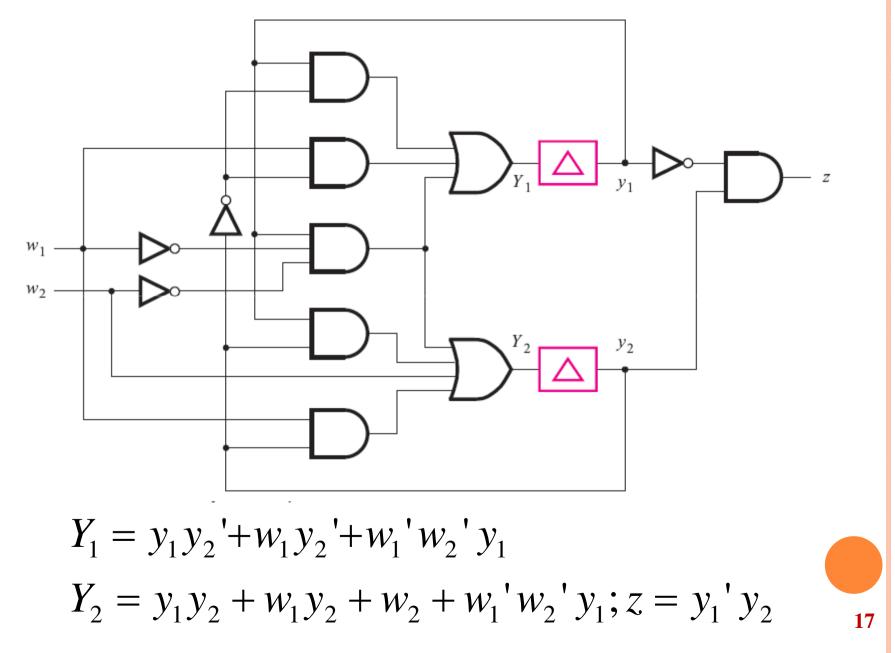

#### **FURTHER EXAMPLE (2)**

| Present               | ]              |           |           |           |        |

|-----------------------|----------------|-----------|-----------|-----------|--------|

| state                 | $w_2 w_1 = 00$ | 01        | 10        | 11        | Output |

| <i>Y</i> 2 <i>Y</i> 1 | $Y_2 Y_1$      | $Y_2 Y_1$ | $Y_2 Y_1$ | $Y_2 Y_1$ | Z      |

| 00                    | 00             | 01        | 10        | 11        | 0      |

| 01                    | 11             | 01        | 11        | 11        | 0      |

| 10                    | 00             | 10        | (10)      | (10)      | 1      |

| 11                    | (11)           | 10        | 10        | 10        | 0      |

#### (a) Excitation table

| Present | Next state       |       |            | Output |

|---------|------------------|-------|------------|--------|

| state   | $w_2w_1 = 00  0$ | 1 10  | 11         | Ζ      |

| А       | A E              | C C   | D          | 0      |

| В       | D (E             | b) D  | D          | 0      |

| С       | A (              | ) (c) | $\bigcirc$ | 1      |

| D       | D C              | C     | С          | 0      |

(b) Flow table

#### FURTHER EXAMPLE (3)

| Present | Next s           | state  |            | Output |

|---------|------------------|--------|------------|--------|

| state   | $w_2 w_1 = 00$ ( | 01 10  | 11         | Z      |

| А       | (A) 1            | B C    | Ι          | 0      |

| В       | D (1             | B) –   | D          | 0      |

| С       | Α (              | C) (C) | $\bigcirc$ | 1      |

| D       | D                | C C    | С          | 0      |

<u>Unspecified entries</u>: At state B: stable with input  $w_2w_1=01$ . Thus, cannot achieve  $w_2w_1=10$ . (2 inputs cannot change at the same time.)

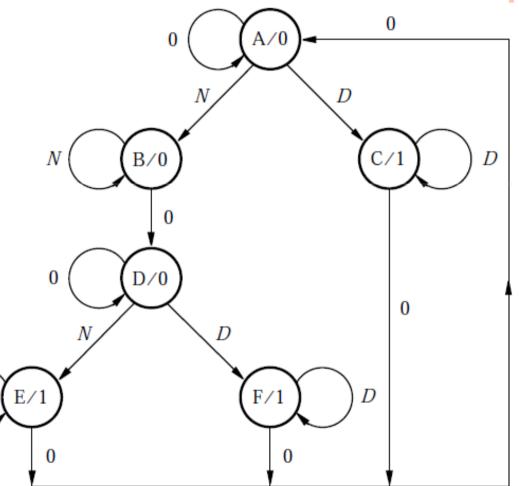

Synthesis of Asynchronous Circuits

the same basic steps used to synthesize the synchronous circuits

- **1**. Devise a state diagram for an FSM

- 2. Derive the flow table and reduce the number of states if Possible

- **3**. Perform the state assignment and derive the excitation table

- 4. Obtain the next-state and output expressions

- 5. Construct a circuit that implements these expressions

- Reverse of Analysis

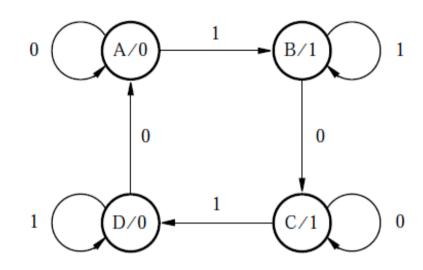

**EXAMPLE: SERIAL PARITY GENERATOR**

- input w : pulses are applied to w

- ✤output z

- ✤z=1 if the number of previously applied pulses is odd

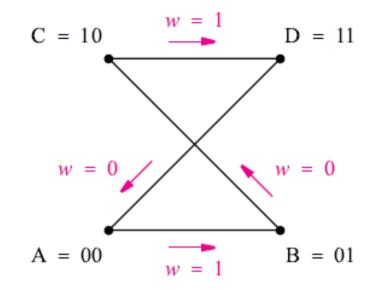

#### **EXAMPLE: SERIAL PARITY GENERATOR (2)**

| Present               | Next  |       |        |

|-----------------------|-------|-------|--------|

| state                 | w = 0 | w = 1 | Output |

| <i>Y</i> 2 <i>Y</i> 1 | Y     | Ζ     |        |

| 00                    | 00    | 01    | 0      |

| 01                    | 10    | 01    | 1      |

| 10                    | 10    | 11    | 1      |

| 11                    | 00    | (11)  | 0      |

(a) Poor state assignment

Next state

(a) State diagram

| Present | Next  | Output |   |

|---------|-------|--------|---|

| State   | w = 0 | w = 1  | z |

| А       | A     | В      | 0 |

| В       | С     | B      | 1 |

| С       | C     | D      | 1 |

| D       | А     | D      | 0 |

(b) Flow table

| Present               | Next      |       |        |  |

|-----------------------|-----------|-------|--------|--|

| state                 | w = 0     | w = 1 | Output |  |

| <i>Y</i> 2 <i>Y</i> 1 | $Y_2 Y_1$ |       | Z      |  |

| 00                    | 00        | 01    | 0      |  |

| 01                    | 11        | 01    | 1      |  |

| 11                    | (11)      | 10    | 1      |  |

| 10                    | 00        | (10)  | 0      |  |

## **STATE ASSIGNMENT**

| Present               | Next      |       |        |

|-----------------------|-----------|-------|--------|

| state                 | w = 0     | w = 1 | Output |

| <i>Y</i> 2 <i>Y</i> 1 | $Y_2 Y_1$ |       | Z      |

| 00                    | 00        | 01    | 0      |

| 01                    | 10        | 01    | 1      |

| 10                    | (10)      | 11    | 1      |

| 11                    | 00        | (11)  | 0      |

(a) Poor state assignment

| Present               | Next      | Output |        |

|-----------------------|-----------|--------|--------|

| state                 | w = 0     | w = 1  | Output |

| <i>Y</i> 2 <i>Y</i> 1 | $Y_2 Y_1$ |        | Ζ      |

| 00                    | 00        | 01     | 0      |

| 01                    | 11        | (01)   | 1      |

| 11                    | (11)      | 10     | 1      |

| 10                    | 00        | (10)   | 0      |

- State assignment (a) has a major flaw

- $\mathbf{ \stackrel{\bullet}{\bullet}} y_2 y_1 = 11 \rightarrow y_2 y_1 = 00$

- the values of the next-state variables determined by the networks of logic gates with varying delays

- $\succ$  suppose  $y_1$  changes first

- $y_2 y_1 = 10 \rightarrow \text{state C}(10)$

- ☆ state C is stable when w=0

- $\succ$  suppose y<sub>2</sub> changes first

- \*  $y_2y_1=01 > state B (01)$

- \* try to change to  $y_2y_1=10$  when w=0

- \* if  $y_1$  changes first,  $y_2y_1=00$

- ➤ race condition occurs

#### **RACE CONDITION**

A race is said to occur if between next set of states  $S_{\alpha}$  and present states  $s_{\alpha}$ , there are two or more bits change (two or more latches undergoes change in Q output) at the memory or delay section. Race condition arises due to variable number of delays of different latches, which lead to intermediate states.

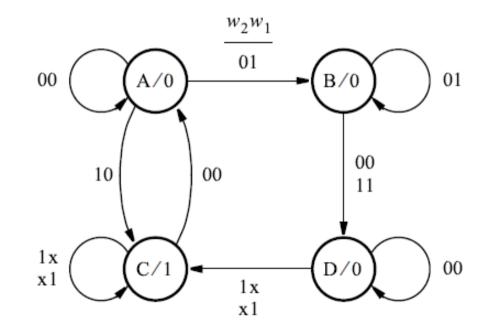

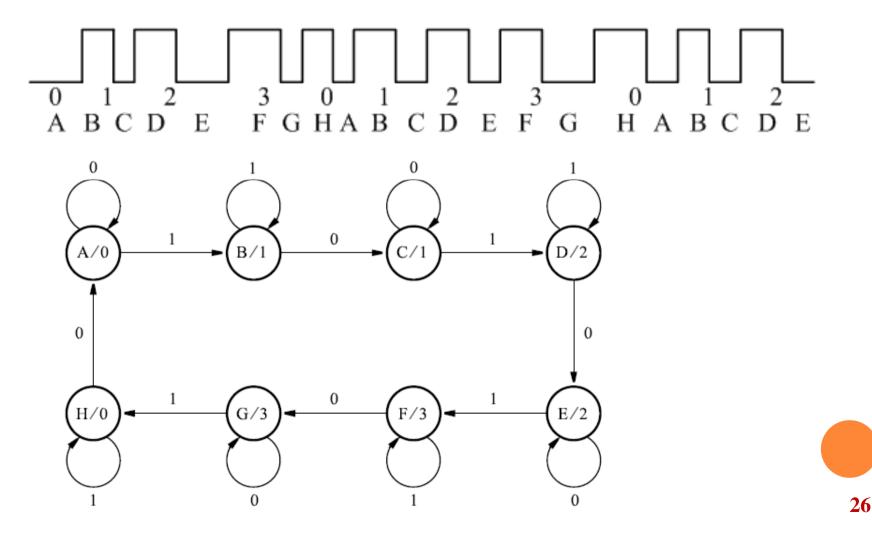

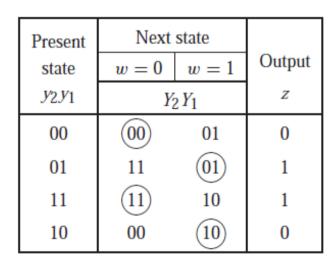

**MODULO-4 UP COUNTER**

**♦**Input w: 1 cause  $A \rightarrow B$ , and stay there. **♦**w=0 cause  $B \rightarrow C$  and so on

## **FLOW TABLE & EXCITATION TABLE**

| Present | Next  | state          | Output |

|---------|-------|----------------|--------|

| state   | w = 0 | w = 1          | Z      |

| А       | (A)   | В              | 0      |

| В       | С     | B              | 1      |

| С       | C     | D              | 1      |

| D       | Е     | D              | 2      |

| Е       | E     | F              | 2      |

| F       | G     | F              | 3      |

| G       | G     | Н              | 3      |

| Н       | А     | $(\mathbf{H})$ | 0      |

| Present                          | Next  |         |        |

|----------------------------------|-------|---------|--------|

| state                            | w = 0 | w = 1   | Output |

| <i>Y</i> 3 <i>Y</i> 2 <i>Y</i> 1 | $Y_3$ | z2z1    |        |

| 000                              | 000   | 001     | 00     |

| 001                              | 011   | 011 001 |        |

| 011                              | 011   | 010     | 01     |

| 010                              | 110   | 010     | 10     |

| 110                              | (110) | 111     | 10     |

| 111                              | 101   | (111)   | 11     |

| 101                              | (101) | 100     | 11     |

| 100                              | 000   | 100     | 00     |

(a) Flow table

(b) Excitation table

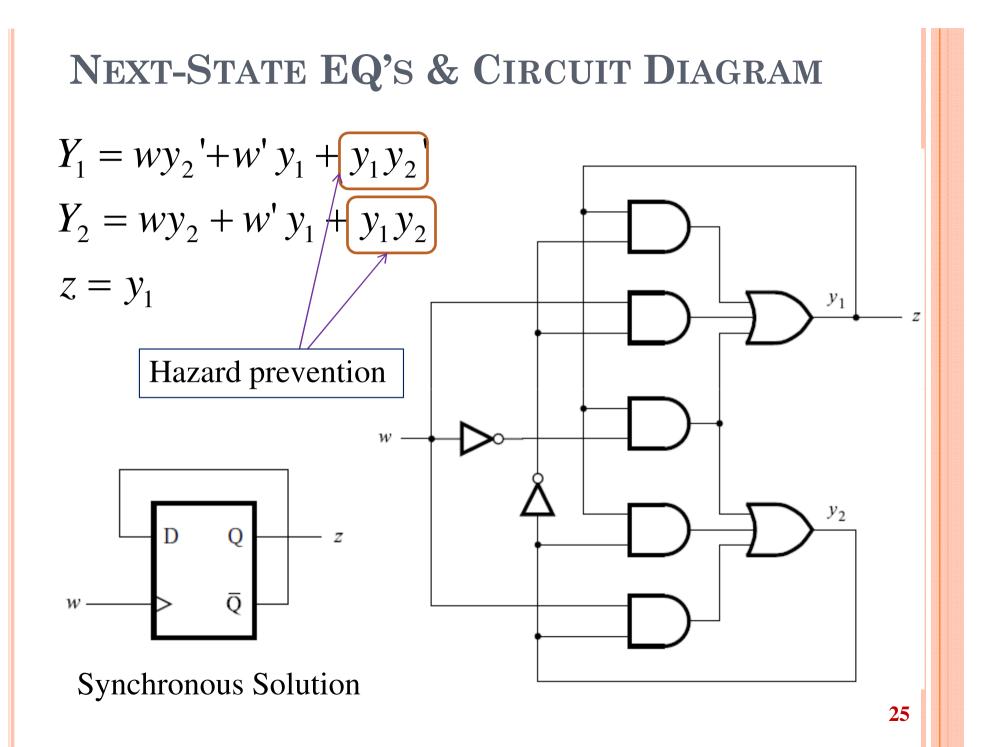

NEXT STATE & OUTPUT EQ'S

$$Y_1 = w' y_1 + wy_2 y_3 + wy_2' y_3' + y_1 y_2 y_3 + y_1 y_2' y_3$$

$Y_2 = wy_2 + w' y_1 y_3' + y_1' y_2 + y_2 y_3'$

$Y_3 = wy_3 + y_1 y_3 + y_1' y_2 w' + y_2 y_3$

$z_1 = y_1$

$z_2 = y_1 y_3 + y_1' y_2$

Exercise: Draw the circuit diagram.

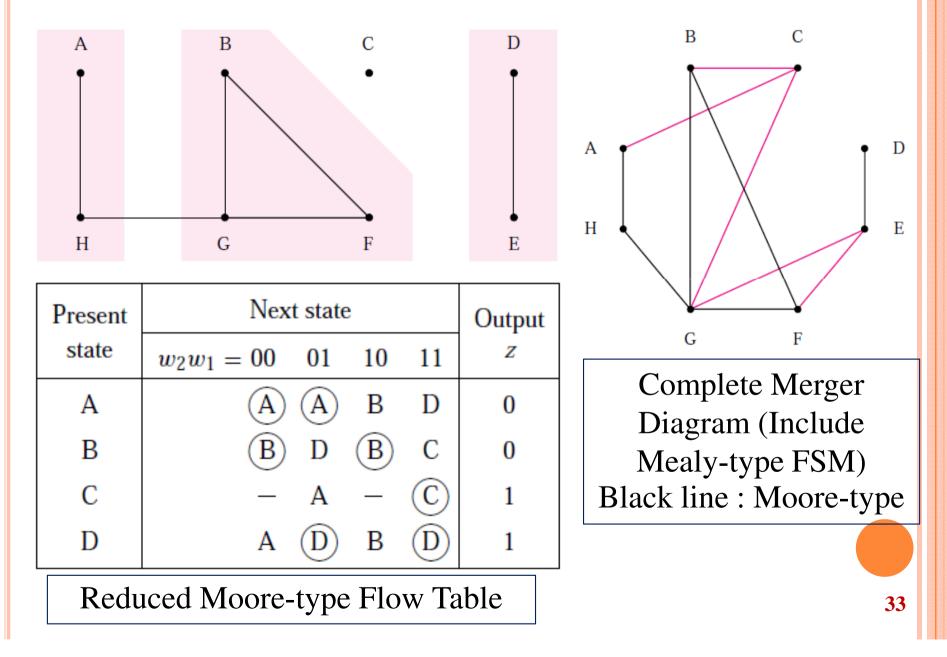

#### **STATE REDUCTION**

# For simpler implementation (fewer FF's and so on)

# Two step approach

Partitioning (Same as the synchronous case)

\*Equivalent states : equivalent k-successors and equivalent stable next-state with same input.

≻Use merger diagram

#### **COMPATIBILITY OF STATES**

- <u>Definition</u>: Two states (rows in a flow table),  $S_i$  and  $S_j$ , are said to be compatible if there are no state conflicts for any input valuation. Thus for each input valuation, one of the following conditions must be true:

- \*both  $S_i$  and  $S_j$  have the same successor, or \*both  $S_i$  and  $S_j$  are stable, or

- $\bullet$  the successor of  $S_i$  or  $S_j$ , or both, is unspecified.

- Moreover, both  $S_i$  and  $S_j$  must have the same output whenever specified.

#### **COMPATIBLE STATES EXAMPLE**

| Present | Next state     |     |    |            | Output |

|---------|----------------|-----|----|------------|--------|

| state   | $w_2 w_1 = 00$ | 01  | 10 | 11         | Ζ      |

| А       | A              | Н   | В  | _          | 0      |

| В       | F              | _   | B  | С          | 0      |

| С       | _              | Н   | —  | $\bigcirc$ | 1      |

| D       | А              | D   | —  | E          | 1      |

| E       | _              | D   | G  | E          | 1      |

| F       | F              | D   | _  | _          | 0      |

| G       | F              | _   | G  | _          | 0      |

| Н       | _              | (H) | _  | E          | 0      |

Primitive Flow Table

Compatible pairs: (A,H), (B,F), (B,G), (D,E), (F,G), (G,H).

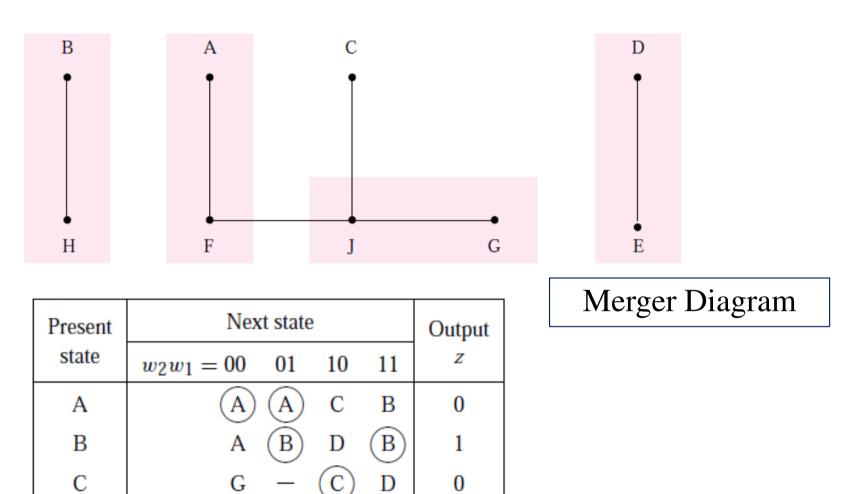

#### MERGER DIAGRAM

- Used to represent the *compatibility* relationship.

- Procedure

- Each row of the flow table is represented as a point, labeled by the name of the row.

- >Aline is drawn connecting any two points that correspond to compatible states (rows).

The reduced flow table can be derived from the merger diagram by choosing the "best" merging possibility.

#### MERGER DIAGRAM FOR PREVIOUS COMPATIBLE STATES EXAMPLE

# **STATE REDUCTION PROCEDURE**

- 1. Use the partitioning procedure to eliminate the equivalent states in a primitive flow table.

- 2. Construct a merger diagram for the resulting flow table.

- 3. Choose subsets of compatible states that can be merged, trying to minimize the number of subsets needed to cover all states. Each state must be included in only one of the chosen subsets.

- 4. Derive the reduced flow table by merging the rows in chosen subsets.

- 5. Repeat steps 2 to 4 to see whether further reductions are possible.

#### **STATE REDUCTION EXAMPLE 1**

| Present | Next state     |    |                |                | Output |

|---------|----------------|----|----------------|----------------|--------|

| state   | $w_2 w_1 = 00$ | 01 | 10             | 11             | Z      |

| А       | A              | F  | С              | _              | 0      |

| В       | А              | B  | —              | Н              | 1      |

| С       | G              | _  | $\bigcirc$     | D              | 0      |

| D       | _              | F  | _              | $\bigcirc$     | 1      |

| Е       | G              | —  | E              | D              | 1      |

| F       | _              | F  | _              | Κ              | 0      |

| G       | G              | В  | J              | —              | 0      |

| Н       | _              | L  | Е              | $(\mathbf{H})$ | 1      |

| J       | G              | —  | $(\mathbf{J})$ | _              | 0      |

| К       | _              | В  | Е              | K              | 1      |

| L       | А              |    | _              | Κ              | 1      |

$P_{1} = (AG)(BL)(C)(D)(E)(F)(HK)(J)$  $P_{2} = (A)(G)(BL)(C)(D)(E)(F)(HK)(J)$  $P_{3} = P_{2}$

| Present | Next state     |    |                |                | Output |

|---------|----------------|----|----------------|----------------|--------|

| state   | $w_2 w_1 = 00$ | 01 | 10             | 11             | Z      |

| А       | A              | F  | С              |                | 0      |

| В       | А              | B  | _              | Н              | 1      |

| С       | G              | _  | $\bigcirc$     | D              | 0      |

| D       | _              | F  | _              | $\bigcirc$     | 1      |

| Е       | G              | —  | E              | D              | 1      |

| F       | _              | F  | _              | Н              | 0      |

| G       | G              | В  | J              | _              | 0      |

| Н       | —              | В  | Е              | $(\mathbf{H})$ | 1      |

| J       | G              | _  | $(\mathbf{J})$ | _              | 0      |

## **STATE REDUCTION EXAMPLE 1 (2)**

G

G

D

G

А

В

D

G

D

1

0

**Reduced Flow Table**

## **STATE REDUCTION EXAMPLE 1 (3)**

| Present | Nex            | Output |            |            |   |

|---------|----------------|--------|------------|------------|---|

| state   | $w_2 w_1 = 00$ | 01     | 10         | 11         | Ζ |

| А       | A              | (A)    | С          | В          | 0 |

| В       | А              | B      | D          | B          | 1 |

| С       | C              | В      | <b>(C)</b> | D          | 0 |

| D       | C              | А      | D          | $\bigcirc$ | 1 |

Finalized Flow Table

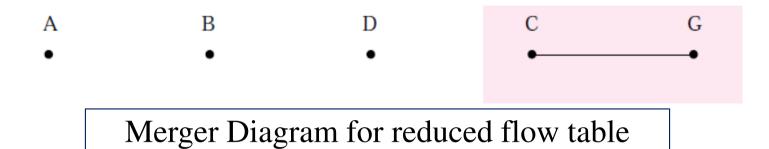

**STATE REDUCTION EXAMPLE 2**

| Present | Nex            | Next state |            |                |   |  |  |  |  |  |

|---------|----------------|------------|------------|----------------|---|--|--|--|--|--|

| state   | $w_2 w_1 = 00$ | 01         | 10         | 11             | Z |  |  |  |  |  |

| Α       | A              | В          | С          |                | 0 |  |  |  |  |  |

| В       | F              | B          | —          | Н              | 0 |  |  |  |  |  |

| С       | F              | _          | $\bigcirc$ | Н              | 0 |  |  |  |  |  |

| D       | D              | G          | С          | —              | 1 |  |  |  |  |  |

| Е       | A              | E          | _          | Н              | 0 |  |  |  |  |  |

| F       | F              | Е          | С          |                | 0 |  |  |  |  |  |

| G       | D              | G          | _          | Н              | 0 |  |  |  |  |  |

| Н       | _              | G          | С          | $(\mathbf{H})$ | 1 |  |  |  |  |  |

|         |                |            |            |                |   |  |  |  |  |  |

$P_1 = (AF)(BEG)(C)(D)(H)$  $P_2 = (AF)(BE)(G)(C)(D)(H)$  $P_3 = P_2$

| Present | Nex            | Output |            |                |   |

|---------|----------------|--------|------------|----------------|---|

| state   | $w_2 w_1 = 00$ | 01     | 10         | 11             | Z |

| А       | A              | В      | С          | _              | 0 |

| В       | А              | B      | _          | Н              | 0 |

| С       | А              | _      | <b>(C)</b> | Н              | 0 |

| D       | D              | G      | С          | _              | 1 |

| G       | D              | G      | —          | Н              | 0 |

| Н       | _              | G      | С          | $(\mathbf{H})$ | 1 |

## **STATE REDUCTION EXAMPLE 2 (2)**

#### Merger Diagram

| Present | Next state                                       | Output z |    |    |    |

|---------|--------------------------------------------------|----------|----|----|----|

| state   | $w_2 w_1 = 00  01  10  11$                       | 00       | 01 | 10 | 11 |

| А       | (A) $(A)$ $(A)$ $(D)$                            | 0        | 0  | 0  | _  |

| D       | $\bigcirc$ $\bigcirc$ $\land$ $\land$ $\bigcirc$ | 1        | 0  | —  | 1  |

Reduced Flow Table

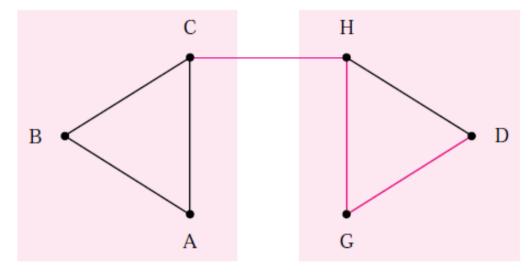

## AN ASYNCHRONOUS VENDING MACHINE

- <u>Specification</u> A candy vending machine with

- accepts only nickels and dimes

- 10 cents for 1 candy

Ν

<u>No change</u> given.

**Initial State**

Diagram

# AN ASYNCHRONOUS VENDING MACHINE (2)

|         | 1       |            |    |    |   | 1 |  |  |  |

|---------|---------|------------|----|----|---|---|--|--|--|

| Present | Ne      | Next state |    |    |   |   |  |  |  |

| State   | DN = 00 | 01         | 10 | 11 | z |   |  |  |  |

| А       | A       | В          | С  | _  | 0 |   |  |  |  |

| В       | D       | B          | _  | _  | 0 |   |  |  |  |

| С       | А       | _          | C  | _  | 1 |   |  |  |  |

| D       | D       | Е          | F  | _  | 0 |   |  |  |  |

| Е       | А       | E          | _  | _  | 1 |   |  |  |  |

| F       | А       | _          | F  | _  | 1 |   |  |  |  |

|         |         |            |    |    |   |   |  |  |  |

|         |         |            |    |    |   |   |  |  |  |

|         |         |            |    |    |   |   |  |  |  |

|         |         |            |    |    |   |   |  |  |  |

|         |         |            |    |    |   |   |  |  |  |

|         |         |            |    |    |   |   |  |  |  |

|         |         |            |    |    |   |   |  |  |  |

$P_1 = (AD)(B)(CF)(E)$  $P_2 = (A)(D)(B)(CF)(E)$  $P_3 = P_2$

| Present | Ne      | Next state |            |    |   |  |  |  |  |  |

|---------|---------|------------|------------|----|---|--|--|--|--|--|

| state   | DN = 00 | 01         | 10         | 11 | Z |  |  |  |  |  |

| А       | A       | В          | С          | _  | 0 |  |  |  |  |  |

| В       | D       | B          | —          | —  | 0 |  |  |  |  |  |

| С       | А       | _          | <b>(C)</b> | —  | 1 |  |  |  |  |  |

| D       | D       | Е          | С          | —  | 0 |  |  |  |  |  |

| Е       | A       | E          | —          | —  | 1 |  |  |  |  |  |

# AN ASYNCHRONOUS VENDING MACHINE (3)

Merger Diagram

| Present | _  | Output |    |            |    |   |

|---------|----|--------|----|------------|----|---|

| state   | DN | = 00   | 01 | 10         | 11 | Z |

| А       |    | A      | В  | С          | _  | 0 |

| В       |    | D      | B  | _          | _  | 0 |

| С       |    | А      | C  | $\bigcirc$ | _  | 1 |

| D       |    | D      | С  | С          | —  | 0 |

Reduced Flow Table

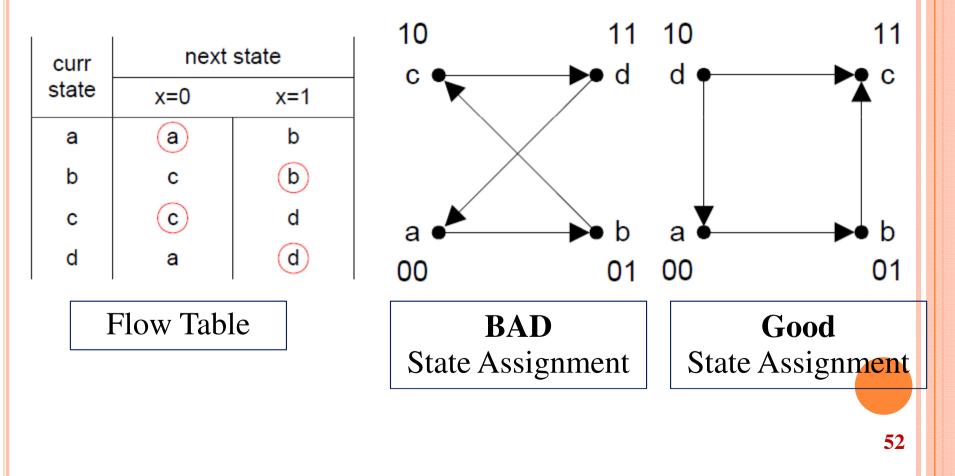

## **STATE ASSIGNMENT**

- To achieve reliable operation of the circuit, the state variables should change their values <u>one at a time</u> in controlled fashion. This can prevent the race.

- ✦Hamming distance : the number of different bits, e.g., 0100,0011 → distance 3.

- Ideal state assignment: Hamming distance of 1 for all transitions from one stable state to another. (may not be possible!!!)

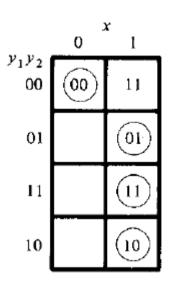

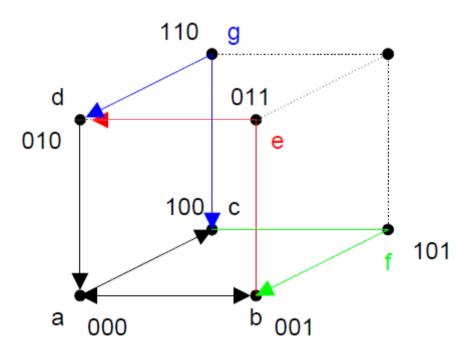

#### **TRANSITION DIAGRAM**

Or state-adjacency diagram, used for depicting the state transitions to provide a convenient aid in searching for a suitable state assignment.

- A good state assignment results if the transition diagram does not have any diagonal paths.

- Condition: Must be possible to *embed* the transition diagram onto a *k*-dimensional cube

#### **TRANSITIONS EXAMPLE**

| Present               | Next          |    |        |

|-----------------------|---------------|----|--------|

| state                 | w = 0 $w = 1$ |    | Output |

| <i>Y</i> 2 <i>Y</i> 1 | Y             | Ζ  |        |

| 00                    | 00            | 01 | 0      |

| 01                    | 10            | 01 | 1      |

| 10                    | 10            | 11 | 1      |

| 11                    | 00 (11)       |    | 0      |

(a) Poor state assignment

(b) Good state assignment

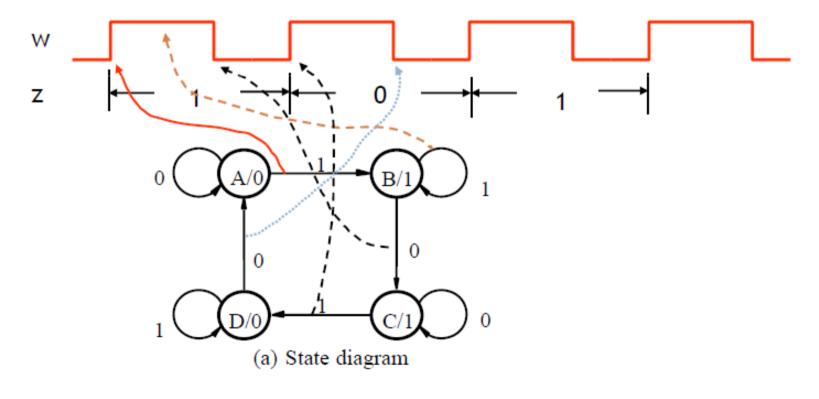

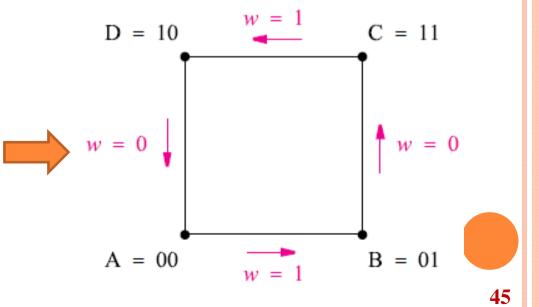

## **RACE CONDITION**

- ✤A <u>race condition</u> occurs in an asynchronous circuit when 2 or more state variables change in response to a change in the value of a circuit input.

- Unequal circuit delays may imply that the 2 or more state variables may not change simultaneously – this can cause a problem.

✤Assume two state variables change...

- ➤ If the circuit reaches the same final, stable state regardless of the order in which the state variables change, then the race in **non-critical.**

- ➤ If the circuit reaches a different final, stable state depending on the order in which the state variables change, then the race is **critical**.

- We need to avoid critical races for predictability and to ensure our circuit does the intended function!

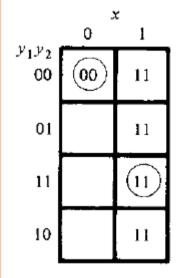

## NON-CRITICAL RACE

♦Assume current state is 00, and input changes from 0 →1. This requires  $y_1y_2$  to change from 00 → 11.

Depending on circuit delays, several possible transition sequences:

- $> 00 \rightarrow 11 \rightarrow 01$  (simultaneous change for y1 and y2).

- > 00 -> 01 (y2 changes first).

- > 00 -> 10 -> 11 -> 01 (y1 changes first)

- In all cases, we end up in the same stable state, so the race is non-critical.

## **CRITICAL RACE**

Assume current state y1y2 is 00, and input changes from 0 > 1. curr state This requires  $y_1y_2$  to change from 00->11. Possible transition sequences: > 00 > 11 (y1 and y2 change simultaneously) > 00 > 01 > 11 (y2 changes first) > 00 > 10 (y1 changes first) ◆So, depending on which state variable changes first, we can get into a different

stable state - the race is critical.

Х

11

11

10

0

00

00

00

00

00

01

11

10

#### **ADDITIONAL EXAMPLE**

Non-critical

- (a) Possible transitions:  $00 \rightarrow 11$   $00 \rightarrow 01 \rightarrow 11$  $00 \rightarrow 10 \rightarrow 11$

- is: (b) Possible transitions:  $00 \rightarrow 11 \rightarrow 01$   $00 \rightarrow 01$   $00 \rightarrow 10 \rightarrow 11 \rightarrow 01$

- (a) Possible transitions:

- 00 → 11

- $\begin{array}{c} 00 \rightarrow 01 \\ 00 \rightarrow 10 \end{array}$

х

1

0

(b) Possible transitions:  $00 \rightarrow 11$

$$00 \rightarrow 01 \rightarrow 11$$

$$00 \rightarrow 10$$

Critical

cal

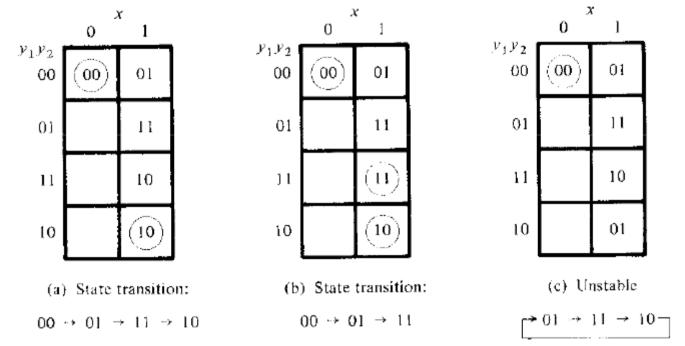

#### CYCLES

A cycle occurs when a circuit goes through a unique sequence of unstable states.

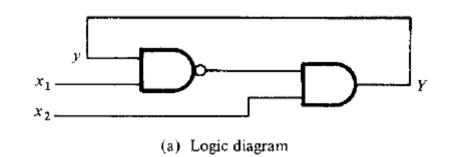

#### INSTABILITY

♦ When

$$x_1x_2=11$$

,  $y=1$ , then  $Y=0$ ,  $Y \neq y$ .

♦ Then  $y=0 \rightarrow Y=1$ ,  $Y \neq y$ .

✤If each gate has a 5-ns propagation delay, Y=0 for 10 ns, and Y=1 for 10 ns, resulting in 50-MHz clock signal!

## **RACE-FREE STATE ASSIGNMENT**

Can prevent races (pre-emptive) by performing state assignment such that transitions from one stable state to another stable state only require one state variable to change at a time.

METHOD ONE FOR RACE FREE STATE ASSIGNMENT

Given a flow table, try and "embed" the symbolic states into the co-ordinates of a "n-dimensional" cube such that the path from stable state to stable state:

Is direct along a single edge of the cube, or

Goes through newly introduced unstable states along edges of the cube.

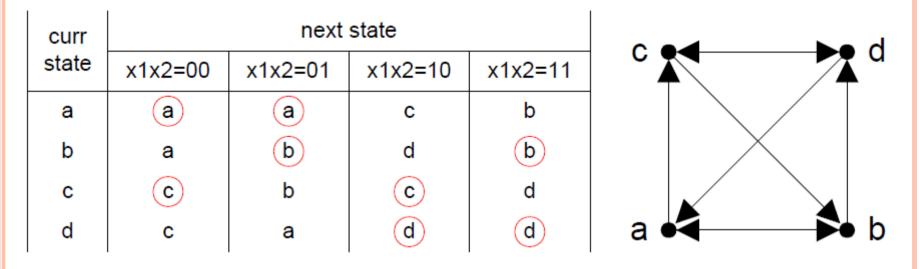

## **METHOD ONE EXAMPLE**

- Can attempt to embed 4 states into a 2dimensional cube and draw the transition diagram:

- >No state assignment that has only one state variable changing at a time.

## **METHOD ONE EXAMPLE (CONT)**

- Solution is to introduce additional, unstable states and use them as "intermediate" states during transitions.

- i.e., embed the 4-states into the corners of a 3-dimensional cube.

## **METHOD ONE EXAMPLE (CONT)**

All transitions are made properly by introducing extra unstable states (Note: the new extra states are always unstable!!!):

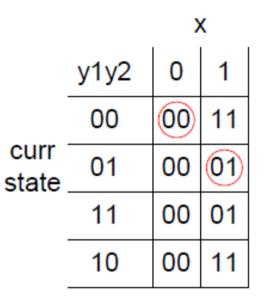

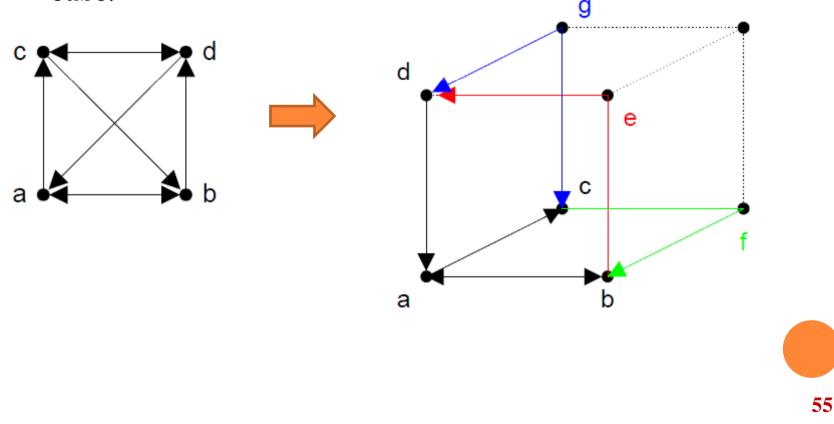

## **EXAMPLE : RACE-FREE FLOW TABLE**

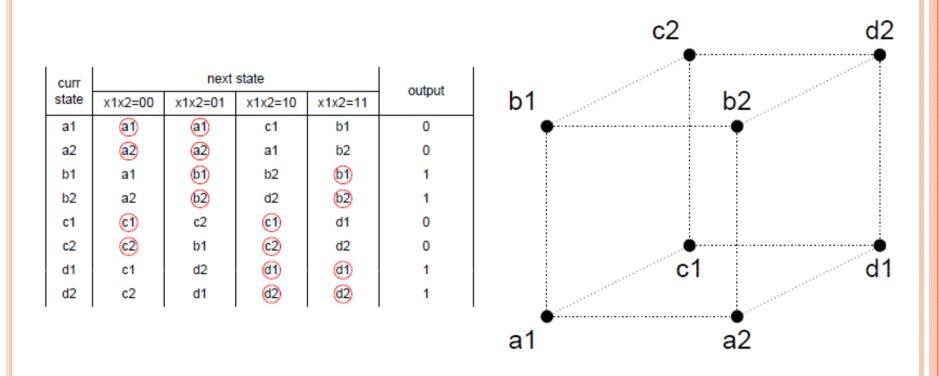

Can now see the original flow table, and an expanded flow table (extra unstable states) that has a race-free state assignment (see previous slide!):

| curr  |         | next    | state   |         |   |       |         |         |         |         |

|-------|---------|---------|---------|---------|---|-------|---------|---------|---------|---------|

| state | x1x2=00 | x1x2=01 | x1x2=10 | x1x2=11 |   |       |         |         |         |         |

| а     | a       | a       | С       | b       |   |       |         |         |         |         |

| b     | а       | b       | d       | b       |   |       |         |         |         |         |

| с     | C       | b       | С       | d       |   |       |         |         |         |         |

| d     | с       | а       | d       | d       |   | curr  |         | next    | state   |         |

| •     |         |         | ·       |         |   | state | x1x2=00 | x1x2=01 | x1x2=10 | x1x2=11 |

|       |         |         |         |         | ſ | а     | a       | a       | с       | b       |

|       |         |         |         |         |   | b     | а       | b       | е       | b       |

|       |         |         |         |         |   | с     | С       | b       | C       | g       |

|       |         |         |         |         |   | d     | g       | а       | d       | d       |

|       |         |         |         | /       |   | е     | -       | -       | d       | -       |

|       |         |         |         |         |   | f     | -       | b       | -       | -       |

|       |         |         |         |         |   | g     | с       | -       | -       | d       |

|       |         |         |         |         |   | '     |         |         | I       |         |

|       |         |         |         |         |   |       |         |         |         | 57      |

METHOD TWO FOR RACE FREE STATE ASSIGNMENT

- Method useful for flow tables with <= 4 states.

- Replace a state with multiple (two) equivalent states

- >Note: Outputs must be the same for the

equivalent states!!!

## **METHOD TWO EXAMPLE**

Consider the following flow table, and another (larger table) with equivalent states:

| curr  |         | next state |         |         |        |  |  |  |  |  |

|-------|---------|------------|---------|---------|--------|--|--|--|--|--|

| state | x1x2=00 | x1x2=01    | x1x2=10 | x1x2=11 | output |  |  |  |  |  |

| а     | a       | a          | С       | b       | 0      |  |  |  |  |  |

| b     | а       | b          | d       | b       | 1      |  |  |  |  |  |

| с     | C       | b          | C       | d       | 0      |  |  |  |  |  |

| d     | с       | а          | d       | d       | 1      |  |  |  |  |  |

|       |         |            |         |         | ·      |  |  |  |  |  |

| curr       |            | next       | state      |            | output |

|------------|------------|------------|------------|------------|--------|

| state      | x1x2=00    | x1x2=01    | x1x2=10    | x1x2=11    | output |

| a1         | <u>a1</u>  | <u>a</u> 1 | c1         | b1         | 0      |

| a2         | <u>a2</u>  | <u>a2</u>  | a1         | b2         | 0      |

| b1         | a1         | 61         | b2         | 61         | 1      |

| b2         | a2         | <u>b2</u>  | d2         | 62         | 1      |

| <b>c</b> 1 | <u>C1</u>  | c2         | <u>C1</u>  | <b>d</b> 1 | 0      |

| c2         | <u>c</u> 2 | b1         | <u>c</u> 2 | d2         | 0      |

| d1         | c1         | d2         | <u>d1</u>  | <u>d1</u>  | 1      |

| d2         | c2         | d1         | <u>d2</u>  | <u>d</u> 2 | 1      |

- The flow table with equivalent states permits a race free state assignment.

- We can see this by looking at the states on a 3-dimensional cube.

#### **METHOD TWO EXAMPLE (CONT)**

With equivalent states, we always have 1 of the 2 equivalent states directly adjacent to every other state! **METHOD THREE FOR RACE-FREE STATE ASSIGNMENT**

- Can use the idea of one-hot encoding to get a race free state assignment...

- ✤Given n-states, let the i<sup>th</sup> state be encoded as 0...010..0 where the 1 is in the i<sup>th</sup> location.

For a transition from i<sup>th</sup> stable state to j<sup>th</sup> stable state, introduce unstable state with encoding 0..010..010..0 where the 1s are in the i<sup>th</sup> and j<sup>th</sup> position.

## **METHOD THREE EXAMPLE**

- Consider the following flow table, with one-hot state assignment:

- Look for transitions and introduce new unstable states, as required using one-hot encoding scheme.

|      | curr  |         | next    | state   |         |      |       |         |         |         |         |

|------|-------|---------|---------|---------|---------|------|-------|---------|---------|---------|---------|

|      | state | x1x2=00 | x1x2=01 | x1x2=10 | x1x2=11 |      |       |         |         |         |         |

| 0001 | а     | a       | a       | с       | b       |      |       |         |         |         |         |

| 0010 | b     | а       | b       | d       | b       |      |       |         |         |         |         |

| 0100 | с     | C       | b       | C       | d       |      | curr  |         | next    | state   |         |

| 1000 | d     | с       | а       | d       | d       |      | state | x1x2=00 | x1x2=01 | x1x2=10 | x1x2=11 |

|      |       |         |         |         |         | 0001 | а     | a       | a       | е       | f       |

|      |       |         |         |         |         | 0010 | b     | f       | b       | g       | b       |

|      |       |         |         |         |         | 0100 | с     | C       | h       | C       | i       |

|      |       |         |         |         |         | 1000 | d     | с       | j       | d       | d       |

|      |       |         |         |         |         | 0101 | е     | -       | -       | с       | -       |

|      |       |         |         |         |         | 0011 | f     | а       | -       | -       | b       |

|      |       |         |         |         |         | 1010 | g     | -       | -       | d       | -       |

|      |       |         |         |         |         | 0110 | h     | -       | b       | -       | -       |

|      |       |         |         |         |         | 1100 | i     | с       | -       | -       | d       |

|      |       |         |         |         |         | 1001 | i     | -       | а       | -       | -       |

#### ASYNCHRONOUS SEQUENTIAL CIRCUITS SUMMARY

## Analysis:

- From the logic diagram, determine input, output, state variable.

- > Derive Boolean functions.

- > Obtain excitation table, flow table, state diagram.

- Synthesis (Design):

- Determine state diagram and primitive flow table.

- $\succ$  Reduce states if possible.

- > Assign states and obtain excitation table.

- > Derive Boolean functions and design circuit.